この世のCPUを食べ尽くすのだ! 第1章 第5節

~あんたCPUなんか創ってどうするのよ?! Vol.3~

2018/10/8

技術書典5 け39

第1章 第5節 ROMとRAMを別々に接続しつつ、アドレス空間を共有する方法

PC向けやスマートフォン向けの高性能なCPUでは当たり前になった方法です。ハーバード・アーキテクチャを採用しつつもノイマン型のようにROMとRAMにシームレスにアクセスできるので、高い性能と高級言語との相性の良さを両立できます。回路が複雑になると言う欠点はありますが、最先端技術を惜しみなく投入して製造される最新のCPUでは問題になりません。

ただし、この方法には2通りの解釈があることに気をつけてください。

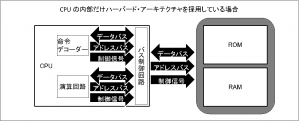

最新のPC向けCPUやスマートフォン向けCPUの場合、CPU内部はハーバード・アーキテクチャになっていてプログラム用の回路とデータ用の回路が分離していますが、CPU外部のROMやRAMへのアクセスは単一の共有バスによって行っています。元々これらのCPUはノイマン型を前提に設計されているので、ROMとRAMは単一のメモリ空間を共有します。そのため厳密な意味ではハーバード・アーキテクチャとは言えません。

図9 CPUの内部だけハーバード・アーキテクチャを採用している場合

いっぽうAVRやPIC18シリーズ以降のように、ハーバード・アーキテクチャでありながらプログラム内からROMにアクセスできるアーキテクチャも存在します。これはCPU内にROM用の回路とRAM用の回路の橋渡しをするブリッジ回路を搭載することで可能となります。このブリッジをもう一歩進めて、ROM用のアドレス空間とRAM用のアドレス空間を共通化すればC言語などの高級言語との相性も劇的に改善されます。ハードウエア的にはROMとRAMは別々の回路に接続されているのですが、CPUの内部で(必要な時だけ)共通化する訳です。

残念ながら筆者が知る範囲では、このようにハーバード・アーキテクチャを採用した上でROMとRAMのアドレス空間を共有化しているCPUは見つけられませんでした。(日立のSHシリーズには同じ思想を感じたのですが。) 結局のところこれは、高級言語との相性は重要視されていないという事なのでしょう。

PICやAVRでprintf()なんか使わねーよ、と言われてしまえばそれまでですが、組み込み系のCPUの性能向上と、それに伴う用途の拡大、プログラマーの世代交代と、それに伴うアセンブラ人口の減少を考えると、このまま放置して良いとは思いません。