この世のCPUを食べ尽くすのだ! 第1章 第2節

~あんたCPUなんか創ってどうするのよ?! Vol.3~

2018/10/8

技術書典5 け39

第1章 第2節 ノイマン型の欠点

ノイマン型にも欠点はあります。それはROMとRAMを同様に扱うことを強要される点です。

例えばテレビやエアコンのリモコンのような、ほとんど何の計算もしない用途を思い浮かべてください。

この場合RAMはほとんど必要ありません。完全にRAMが不要であれば問題は起きないのですが、ほんのちょっとだけ必要な場合には問題が露呈します。

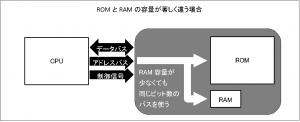

例えばプログラム(つまりROM)が1000バイト、RAMが10バイトだけ必要だとしましょう。するとアドレスバスは最低10ビット必要となります。ROMとRAMが同じ位置に接続されていますから、たった10バイトしかないRAMにアクセスする場合にも10ビットでアドレス指定をする必要があります。もしROMとRAMが分離されていれば、RAMへのアクセスには4ビットのアドレス指定で十分なのですが、ノイマン型ではROMとRAMを同列に扱う必要があるため10ビットのアドレス指定が必要となります。

たかが10ビットくらいでケチケチするなと言う意見もあるでしょう。

しかしARMのThumb命令に代表されるように、同じ作業をするプログラムであればプログラムサイズが小さい方が優れているのです。これはコード効率と呼ばれ、無駄にサイズの大きなプログラムは現代でも好ましくありません。そのため無駄なアドレス指定は無い方が良く、RAM容量が少ないのであれば、アドレス指定のビット数も少ない方が望ましいのです。

話が抽象的になりましたので、ノイマン型を用いてTD4EX3を実現したらどうなるかを検討してみましょう。

例えばRAMから、とあるデータを読み出す場合を考えてみます。

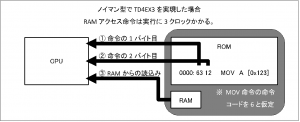

本シリーズのVol.1で製作したTD4EX2ではアドレスバスを12ビットに拡大しましたので、それをベースに作成するTD4EX3でもアドレスバスは12ビットです。ROMとRAMは同じアドレスバスを共有しますから、RAMへのアクセス時にも12ビットのアドレス指定が必要です。ということは、ジャンプ命令が2バイト命令に拡張されているのと同様に、RAMへのアクセス命令も2バイト化する必要があります。そうしないと12ビット分のアドレス指定を命令コードの中に確保できないからです。

そしてもう一つ。ROMとRAMが同じバスを共有しているために、ROMとRAMへの同時アクセスができません。つまり命令フェッチとRAMへの読み書きは別々のタイミングで行う必要があるのです。

元々TD4は1命令1クロックで設計されていました。それを拡張したTD4EX2ではROM容量拡大のためにジャンプ命令(条件ジャンプ命令含む)のみを2バイト化し、2クロックで実行するようにしました。

ところがノイマン型を採用したTD4EX3のRAMアクセス命令は、命令フェッチに2クロック、実行に1クロックの合計3クロックが必要となります。命令フェッチとRAMへのアクセスを同時にできないからです。

これは設計がかなり大変です。

TD4EX2では、TD4で余っていたフリップフロップ(74HC74の半分)を使って2バイト命令を制御しています。しかし実行に3クロック必要となるとフリップフロップでは制御できず、3までカウントできるカウンタICが必要になります。そして1バイト命令を1クロックで実行し、2バイトのジャンプ命令を2クロックで実行し、2バイトのRAMアクセス命令を3クロックで実行するという複雑なCPUとなってしまいます。

さすがにこれは筆者の手に余ります。

C言語などの高級言語の使用が必須なのであれば選択肢に残りますが、今回のプロジェクトではアセンブラ(しかもハンドアセンブル)で十分なので、このノイマン型は不採用とします。