この世のCPUを食べ尽くすのだ! 第1章 第3節

~あんたCPUなんか創ってどうするのよ?! Vol.3~

2018/10/8

技術書典5 け39

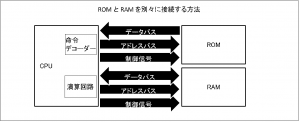

第1章 第3節 ROMとRAMを別々に接続する方法

CPUにRAMを接続する際に、ROMとは別の場所に接続する方法もあります。ハーバード・アーキテクチャなどと呼ばれることもあるので、ご存知の方もいらっしゃるでしょう。

この場合ROMとRAMは別回路になっていれば何でも良く、ハーバード・アーキテクチャの語源となったHarvard Mark IというコンピューターではROMは紙テープ、RAMはリレーだったそうです 。現代のCPUでもハーバード・アーキテクチャは多くのCPUで使われており、有名なところではAtmel社のAVRシリーズやMicrochip社のPICシリーズなどがあります。

このハーバード・アーキテクチャの利点は幾つかあります。

- ROMとRAMへの同時アクセスが可能

ROMとRAMは別回路でCPUに接続されているので、アクセス時に互いが干渉しません。そのためROMからの命令フェッチとRAMへの読み書きを同時に行うことができます。これはTD4の1命令1クロックという設計と相性が良く、TD4EX3に最適です。

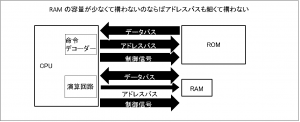

- ROMおよびRAMの容量の自由度の高さ

ROMとRAMが別回路に接続されているため、アドレスバスのビット数を任意に決めることができ、互いに干渉することなく容量を決定できます。

TD4EX3はROMを4KBに拡張したTD4EX2をベースにしています。もしTD4EX3をノイマン型で設計した場合、RAMのサイズはROMのサイズに干渉されます。なぜなら同じアドレスバスを共有するため、ROMとRAMの合計サイズが4KBとなるからです。もしRAMのサイズを1KBにしたならば、ROMの最大サイズは3KBに制限されてしまいます。

しかしROMとRAMが別々の回路に接続されているハーバード・アーキテクチャならば、そのような制限はありません。ROMを何キロバイト搭載しようとも、自由な容量のRAMを搭載できます。そしてRAMに接続するアドレスバスのビット数もROMとは無関係に決定できます。もしRAM容量を256語にするならば8ビットのアドレスバスで十分ですし、逆に16ビットのアドレスバスを採用すれば65536語もの大容量を搭載できます。

本プロジェクトではRAMの容量は少なくて構わないので、この方法は最適です。