FPGAコンフィグレーション・プログラム作成

コンフィグレーション・プログラム作成は、本格的なプログラムになることが予想され、2015年12月の時点ではその作成にはかなり難しい感があった。近年はオープンソースの思想が広まっており、有用なプログラムソースが公開されているためなんとかなるのでは、と考えプログラミングに着手することにした。参考にしたプログラムは、

xilprg

https://sourceforge.net/projects/xilprg/

JTAGプログラミングツールであり、XILINX Parallel IIIケーブル、Digilent USBケーブルをサポートしており C++で記述されている。

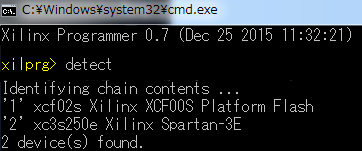

コマンドで操作するタイプで、XILINXの古いFPGAをサポートする他、XILINX製コンフィグレーションROMをサポートしている。FPGA接続状態を検出するコマンド >detect を実行するとデバイス・チェーンの状態を調べることができる。その際、推奨された接続であると コンフィグレーションROMもデバイスのひとつとして表示される。

2つのデバイスが表示されたなら、その一方を選んで書き込み等の操作を行うことになる。

コンフィグレーションの場合は、>program 1 test.bit

でデバイス番号をパラメータとして指定し、書き込むファイル名を次に入力することになる。

xilprg は、クラスの継承や階層構造が明確でSTLコンテナを駆使したプログラミングは一見見通しが良い。しかし肝心のJTAG 関連の関数や FPGAを直接アクセスする部分は、ドキュメント等がなかったため、かなり難解であった。

後日、CQ出版 坂巻佳壽美著[JTAGテスト基礎と応用」(以下JTAG本)を手に入れたが、先に読んでおいたhぽうが良かった思う反面、プログラム解析する前では本の内容理解に苦労したかもしれない。

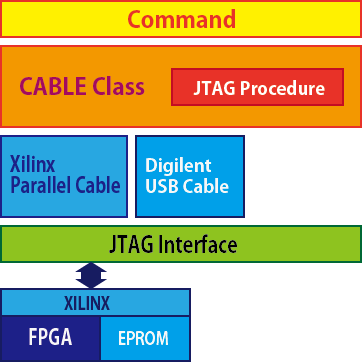

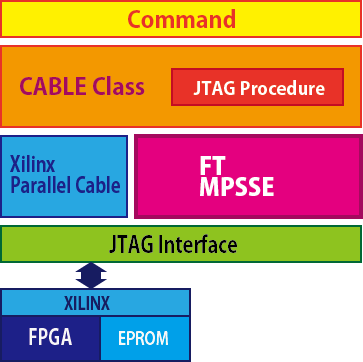

xilprg クラス階層

xilprgのプログラムの階層構造は、クラスがキレイに構築されているおり、CABLEクラスから

・XILINX Parallel IIIケーブル・クラス

・Digilent USBケーブル・クラス

が継承されており、ポリモーフィズムにより、CABLEオブジェクトからのメソッド呼び出しで適したケーブルの処理が行われるようになっている。

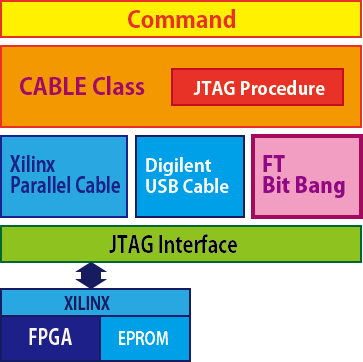

FT2232DのBitBang で対応

FT2232D用のクラスとメソッドを CABLEクラスからの継承としてプログラミングすれば、他の上位ぼ処理は変更せずに目的の動作が期待できるはずである。

FT2232Dの非同期Bit-Bang処理を使ってパラレルケーブルの処理を参考にTCK,TDI,TMS,TDOの各ポートの処理を記述してみた。

するとスンナリと動作し、コマンドラインでFPGA_BASE拡張基板経由でXILINXのFPGAへのコンフィグレーションが可能になった。

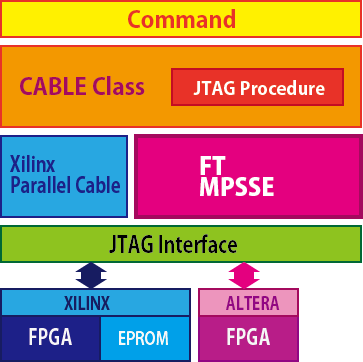

継承クラスを追加した階層

しかし、ここで大きな問題が生じた。スピードが遅すぎる。

1000 ビット/秒程度がやっとで書き込みに10分以上を要してしまう。これでは使い物にならないので他の方法を考えることにする。

FT2232には、クロック同期式シリアルインターフェースであるMPSSE(Multi Protocol Synchronus Serial Engine)機能を有している。JTAGインターフェイスの他SPI、I2C通信を行うことがきる優れた機能であり、FT2232Dでは最高クロックが6MHzが可能であり、通信のやりとりを除いても5Mビット/秒以上の転送速度を実現できるはずである。。MPSSEは、FT2232/FT4232のみが持っている機能だったが最近登場した1chのFT232HLにもこの機能がついている。

FTDI社の提供するドライバAPIを使うことで機能を実現するのであるが、これは試行錯誤の連続でテストプログラムを書きながら適切に動作するAPIの組み合わせを決めていった。処理の部分をMPSSEクラスにまとめ、CABLEクラスに継承するようにして、高速な動作を実現した。

ALTERA Cyclone 対応

ALTERA Cyclone対応を行うことにした。XILINXAとALTERAのFPGAでは、そのアクセス方法が大きく異なり、その方法についてのドキュメントもない。手がかりはALTERA社で配布している JRUNNERのソースプログラム程度である。

xilprgとは、大きく異なるため、ALTERA Cycloneへのアクセスルーチンは、ゼロから書き直すことになり、MPSSEクラスのメソッドから使えるようにするため、プログラムソース全体を大きく書き換える必要があった。さらに、チップの初期データのフォーマットもXILINXとALTERAのチップで共通に使えるようにフォーマットを変更する必要があった。

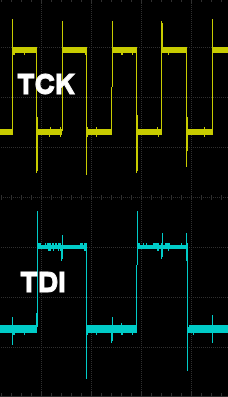

いざ完成して動作させると動作が不安定で、正確性に欠ける。同じ内容のはずの2枚のFPGA_BASEボードでもエラー率の差違がみられ、全体的に安定した動作をさせることができなかった。デジタルオシロでJTAG信号を調べてみると、

TDI信号に大きめのオーバーシュート・アンダーシュートが発生し、信号波形が安定していないことが判明した。ロジックIC 74VHC125との間に220Ω(100Ωだと不足気味)のダンピング抵抗を追加すると、問題が一気に解決した。

ハードウェアを操作するソフトウェアは、ハードの特性とその動きを調べることが如何に重要かということを再認識することになったわけである。