あなたCPUなんか創ってどうするのかしら?! 第3章

~あんたCPUなんか創ってどうするのよ?! Vol.4~

2019/4/14

技術書典6

池袋サンシャインシティ 文化会館ビル2F 展示ホールD「う11」

第3章 TD4EX4のハードウエア

前ページ見開きにTD4EX4の初期リビジョンの回路図を掲載します。

この初期リビジョンで実際に様々テストを行ったところ、いちおうRAMへのアクセスや加減算は出来るものの、幾つかのバグがあり、修正が必要であることが分かりました。

また、回路図全体を見るとANDやORがあまりにも多く、工夫すればICの数を減らせそうな気がします。特に命令デコーダーには74HC00と74HC10と74HC32が使われているにもかかわらず、求められている機能はさほど難しくありません。そこで回路をさらに単純化して使用IC数を減らすべく、あれこれ試行錯誤をすることにしました。

第3章 第1節 キャリーフラグの変更抑制のバグ

本プロジェクトではこれまで3種類のCPUを設計・製作してきました。それらのうちTD4EX2とTD4EX3はジャンプ命令(JMP命令とJNC命令)を可変長命令化しており、それら(特にJNC命令)を正常に動作させるためにキャリーフラグを変更しない回路を追加していました。

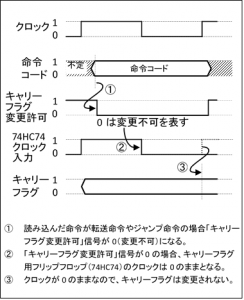

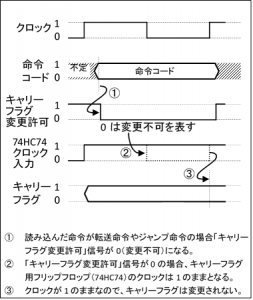

図13 TD4EX2およびTD4EX3のキャリーフラグ変更抑制タイミング(失敗バージョン)

ところが詳細なテストをしてみたところ、このキャリーフラグの変更抑制回路は不十分だという事が分かりました。JNC命令は正常に動作するものの、実行後のキャリーフラグは0にクリアされてしまうのです。他の命令も同様で、全ての命令でキャリーフラグがクリアされてしまう事が分かりました。

つまりTD4EX2やTD4EX3はバグっているのです。いわゆるエラッタという奴です。

困ったのはここからです。

なぜバグっているのか筆者には全く理解できなかったのです。回路図を何度調べても、真理値表を書いてみても、実際の回路をテスターで調べても、全く分かりませんでした。分かったことは、私の意図とは違う動作をしている事だけでした。

おそらくハードウエアに詳しい諸兄ならば、回路図を見ただけで瞬時に気付いたことでしょう。しかし情けないことに筆者が原因を突き止めるまでにはかなりの時間がかかりました。

結局、原因はタイミングでした。

分かってしまえば簡単な事です。キャリーフラグの変更抑制は、フリップフロップのクロックを停止させることで行っているのですが、これにはクロックを0の状態に固定することで停止させるか、1に固定させることで停止するかの2通りがあります。筆者は最初1に固定するように設計したのですが、それでは正しくクロックを停止できない事が分かりました。

脳みその切り替えに時間がかかったのですが、結局クロックを0に固定するように回路を修正した結果、正しくキャリーの変更を抑制できるようになりました。原因が分かった時にはかなり凹みましたが、最終的にはIC数を増やさずに修正できました。

TD4EX4では加減算命令を実行した時だけキャリーフラグが変更されます。