あなたCPUなんか創ってどうするのかしら?! 第2章 第7節

~あんたCPUなんか創ってどうするのよ?! Vol.4~

2019/4/14

技術書典6

池袋サンシャインシティ 文化会館ビル2F 展示ホールD「う11」

第2章 第7節 RAMへの書き込みの制御

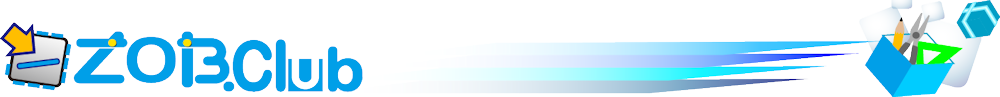

RAMへの書き込み命令は例外扱いなので、真面目に命令コードをデコードして必要な制御を行います。以下にRAM関連回路のブロック図を示します。

図11 RAM関連回路のブロック図

第1章の第8節でも検討ましたが、RAMへの書き込みを行うには以下の処理が必要です。

- アキュムレーターからデータを読み出す。

- ROMの下位4ビットはアキュムレーターと加算しない。

- 演算結果をPCに格納するのを止める。

- 演算結果をI/Oユニットへ送信する。

- キャリーフラグを変更しない

- RAMへの書き込みを行う(読み出しを行わない)。

これらのうち①と③についてはアーキテクチャ設計の段階で完了していますし、②についても第2節で完了していますので、検討する必要があるのは④と⑤と⑥です。⑤のキャリーフラグについては次節で説明しますので、ここでは④と⑥について検討します。基本的にはTD4EX3をと同じです。

第2章 第7節 第1項 RAMの書き込み制御信号

前作Vol.3の「この世のCPUを食べ尽くすのだ!」で実現している通り、RAMへの書き込みはCS制御モードで行います。CS制御モードでは先にRAMのWE信号を0にしておき、あとからCS信号を0にする決まりになっています。そのためTD4EX3およびTD4EX4ではRAMへの書き込み命令が読み込まれると、直ちにI/OユニットへWRITE信号を出力します。I/Oユニット側ではCPUからのWRITE信号とRAMのWE信号が直結されていて、WRITE信号が0になると自動的にWE信号も0になります。

RAMへの書き込み命令の命令コードは1010と1011ですから、論理式は以下のようになります。負論理なので注意してください。

数式10 RAMの書き込み制御信号

WRITE信号 = (NOT bit7) OR bit6 OR (NOT bit5)

第2章 第7節 第2項 I/Oユニットへのデータの出力

RAMに書き込むデータはデーバスを通じてCPUからRAMに送られます。TD4EX3およびTD4EX4はメモリマップドI/Oを採用しているため、テンキーや7セグメントLEDへの出力も同様にデータバス経由でデータを送ります。

データバスは通常はハイインピーダンス状態になっていて、CPUもI/Oユニットもデータを出力しません。ただしそのままだとデータバスの信号が安定しないため、10kΩの抵抗を使ってプルアップしています。

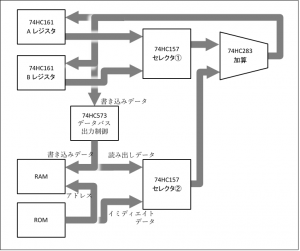

ともあれ、未使用時に不要なデータを出力しないように、TD4EX3とTD4EX4では74HC573を使用してデータ出力を制御しています。これはTD4の出力ポートをデータバス用に変更したものです。詳しくはVol.3である「この世のCPUを食べ尽くすのだ!」をご覧ください。

この出力制御用の74HC573はOutput Control端子(OC端子)によってI/Oユニットへの出力を制御します。通常は1にしておき、出力端子をハイインピーダンス状態にします。I/Oユニットへの出力を行うときは0にすることで、データバスへの出力を行います。

実際にはクロックが0の時だけデータ出力を行うので、論理式は以下のようになります。

数式11 74HC573の出力制御端子(OC)

OC信号 = (NOT bit7) OR bit6 OR (NOT bit5) OR CLOCK