あなたCPUなんか創ってどうするのかしら?! 第2章 第2節

~あんたCPUなんか創ってどうするのよ?! Vol.4~

2019/4/14

技術書典6

池袋サンシャインシティ 文化会館ビル2F 展示ホールD「う11」

第2章 第2節 演算対象を選択するセレクタ②の追加

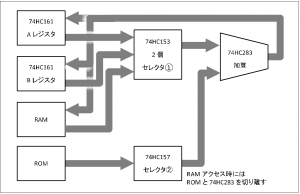

TD4では加算用ICである74HC283には直接ROMが接続されていました。そのため常に命令コードの下位4ビットとの加算を行っています。加算をしたくない場合には0との加算を行わせることで、加算していないかのように見せかける必要がありました。

いっぽうRAMへのアクセスが可能なTD4EX3では命令コードの下位4ビットをRAMのアドレス指定に使用します。そのためRAMへのアクセス時にはROMと74HC283とを切り離す必要があり、図6のように無駄にセレクタ②を追加する羽目になりました。

TD4EX4でもTD4EX3と同様にセレクタ②を使用しますが、その目的はRAMと74HC283の切り離しだけではなく、加算対象の選択も行います。表1の命令コード表を見れば分かるように、TD4EX4ではイミディエイトデータとの加算とRAMとの加算の両方をサポートします。そのため74HC283に供給する加算対象をセレクタ②によって切り替えるようにしています。

この切り替えは命令コードのbit5によって行います。

数式4 セレクタ②の制御信号1

セレクト入力 = bit5

いっぽうストローブ入力はどうなるのかと言うと、通常は0で、RAMへの書き込み命令の時だけ1にする必要があります。これは命令コードの上位4ビットが1010もしくは1011の時に行います。

数式5 セレクタ②の制御信号2

ストローブ入力 = bit7 AND (NOT bit6) AND bit5

実際の回路については他の回路と合わせて検討します。