あなたCPUなんか創ってどうするのかしら?! 第2章 第1節

~あんたCPUなんか創ってどうするのよ?! Vol.4~

2019/4/14

技術書典6

池袋サンシャインシティ 文化会館ビル2F 展示ホールD「う11」

第2章 第1節 アキュムレーター用セレクタの変更

アーキテクチャの設計の段階ではジャンプ命令から検討を始めましたが、論理設計ではアキュムレーターであるAレジスタとBレジスタから検討を始めました。

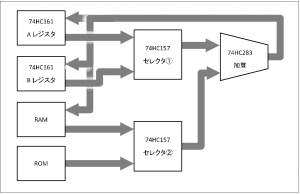

図5にTD4EX4の演算回路のブロック図を示します。TD4EX1と似ていますが、AレジスタとBレジスタが同じセレクタ①に接続されている点が違います。これはTD4EX1ではレジスタ間演算とレジスタ間転送が存在するのに対し、TD4EX4には存在しないためです。

また、TD4EX3と同様に入力ポートもありませんので、セレクタ①はAレジスタとBレジスタの選択だけをすれば良く、TD4で使用していた74HC153は必要ありません。代わりに1個で4ビットの切り替えができる74HC157を使用することができます。これにより使用IC数を1個削減できます。

セレクタ①の制御回路は極めて簡単です。アーキテクチャ設計の段階から回路が簡単になるように考えながら作ってきましたので、74HC157の制御端子には命令コードの信号をそのまま供給すれば良いようになっています。具体的には、命令コードのbit4を74HC157のセレクト入力(後述の回路図ではA/Bと表記)に接続し、bit6をストローブ入力(回路図ではGと表記)に接続すれば完成です。

数式3 セレクタ①の制御信号

セレクト入力 = bit4

ストローブ入力 = bit6