この世のCPUを食べ尽くすのだ! 第2章 第3節

~あんたCPUなんか創ってどうするのよ?! Vol.3~

2018/10/8

技術書典5 け39

第2章 第3節 RAMの概要

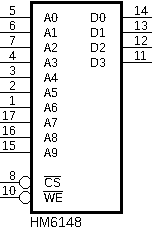

今回使用するRAMはHM6148というICです。これは4ビットのデータを1024個記憶できるSRAMです。18ピンのICとして作られており、データバスは4ビット、アドレスバスは10ビットあります。そして以下の2つの制御信号によってコントロールします。

- CS端子(チップセレクト)

- RAMへのアクセスを制御する入力信号です。負論理なのでCPUから0を与えると、RAM側でデータを出力したり、あるいはデータを記憶したりします。逆にこの信号を1にするとRAMは何もせず、データバスに何も出力しません(ハイインピーダンスになる)。

- TD4EX3との接続ではIN命令またはOUT命令の実行時にCS端子を0にさせます。

- WE端子(ライトイネーブル)

- RAMへの書き込みを制御する入力信号です。これも負論理なのでCPUから0を与えると、RAM側でデータバスから与えられた数値を記憶します。逆にこの信号を1にするとRAMは記憶しているデータをデータバスに出力します。従ってこの端子はIN命令では1に、OUT命令では0にするように回路を設計します。

- このWE端子は単独では動作せず、CS端子と組み合わせて使用します。WE端子を0にした状態でCS端子を0にすると書き込み準備状態となり、CS端子が1に変わった瞬間にデータバスから4ビットのデータを読み込んでRAM内に記憶します。

- 同様にWE端子を1にした状態でCS端子を0にすると読み出し状態となり、RAM内のデータを読み出してデータバスに出力します。この状態はCS端子が1になるまで続きます。

これら2個の制御信号は厳密にタイミングが決められており、データシートに詳細が載っています。このデータシートに沿って回路を正しく設計しないと動作しません。今回TD4EX3を製作するにあたり、一番苦労したのがここです。

以下にHM6148の制御方法を説明します。