この世のCPUを食べ尽くすのだ! 第2章 第3節 第4項

~あんたCPUなんか創ってどうするのよ?! Vol.3~

2018/10/8

技術書典5 け39

第2章 第3節 第4項 WE制御による書き込みの問題点

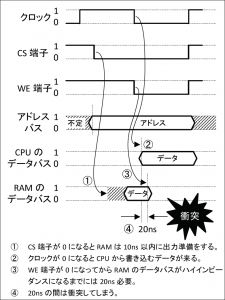

2種類のモードあるRAMへの書き込みですが、TD4EX3の場合にはWE制御モードは使えません。データバスの衝突が起きるからです。

WE制御モードの場合、先にCS端子を0にします。これはRAMからの読み出しを行う状態と同じです。そのためWE制御モードでは、一時的にデータバスにデータが出力される可能性があります。これがCPUから出力されてくる書き込みデータと衝突することになります。

このRAMからの出力データはWE端子が0になってから最大で20ns続きます。そのため衝突を避けるにはCPUからのデータ出力を20ns以上待たせる必要があるのですが、このタイミングの制御はTD4EX3では困難です。

従ってTD4EX3ではCS制御モードでRAMへの書き込みを行います。

なお、データシートによるとCS端子とWE端子が同時に0になった場合でもCS制御モードとして動作することになっていますが、両方の端子を確実に同時に0にする回路を作ろうとするとIC数が増えてしまうので、WE端子を先に0にすることにしました。