この世のCPUを食べ尽くすのだ! 第2章 第3節 第2項

~あんたCPUなんか創ってどうするのよ?! Vol.3~

2018/10/8

技術書典5 け39

第2章 第3節 第2項 通常のRAMからの読み出し

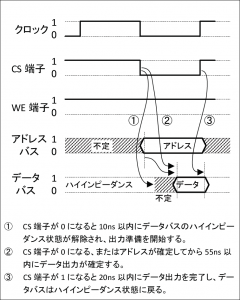

CS端子を制御してRAMからの読み出しを行う方法です。普通はこのモードを使います。

初期状態ではCS端子とWE端子を1にしておきます。この状態ではデータバスにはデータは出力されず、ハイインピーダンス状態になっていますので、例えばCPUとI/Oポートとの間での通信が行われてもRAMは無関係です。

データの読み出しを行う場合、CS端子を0にします。この時、アドレスバスに読み出したいアドレスを指定するのですが、CS端子を0にする前にアドレスを指定しても良いし、0にした後に指定してもかまいません。いずれにせよCS端子とアドレスバスの遅い方から55ns後に、データバスにデータが出力されます。

CPU側でのデータの受け取りが完了したらCS端子を1に戻します。するとRAMはデータの出力を終了させ、20ns以内にデータバスをハイインピーダンス状態に戻します。これで終了です。