この世のCPUを食べ尽くすのだ! 第2章 第1節

~あんたCPUなんか創ってどうするのよ?! Vol.3~

2018/10/8

技術書典5 け39

第2章 第1節 データバスの概要

簡単そうに見えて一番厄介だったのがCPUとI/Oユニットを接続するデータバスの設計です。

TD4には入力用の4ビットのポートと、出力用の4ビットのポートがあり、互いに独立しています。しかし普通のRAMは入力と出力を共有のデータバスで行うので、このままでは接続できません。今回使用するHM6148というRAMも同様で、4ビット幅のデータバス1個で読み出しと書き込みを行います。従ってTD4の入力ポートと出力ポートを繋ぎ合わせて1個のデータバスにする必要があります。

ここで問題となるのが出力ポートに使われている74HC161です。このICは出力を停止する機能が無いため、各ビットが常に1か0の値を出力しています。そのためRAMとの接続には使えません。そのままではRAMからの読み出し時に74H161の出力が衝突してしまうからです。

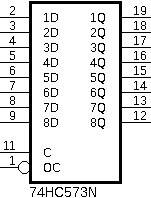

そこで出力ポート用のICを74HC573に変更します。このICは本プロジェクトのVol.1で2バイト命令の1バイト目を保持する目的で使用しましたので慣れています。ただし74HC573は8ビットのラッチなので、そのうちの4ビットだけを使用します。

74HC573が非同期式のレベルトリガであることも重要です。

TD4は1命令1クロックで動作しますが、それを拡張したTD4EX3も原則として同様です。RAMへの書き込みを1クロックで実行するためには、74HC573に入力されたデータがそのまま出力側にスルーされる必要があります。もし74HC161のような同期式のICを使ってしまうと、命令の実行完了時には74HC161への書き込みが行われるだけで、肝心のRAMへの書き込みが行われません。実際のRAMへの書き込みが行われるのは次の命令の実行時になってしまいます。それでは話にならないので、74HC573を使用した上で入力は常にスルー状態にしておき、OUT命令を実行した時だけデータを出力するようにします。

幸いなことに74HC161の書き込み制御信号と74HC573の出力制御信号はどちらも負論理なので、命令デコーダーからの制御信号はそのまま使えます。

実際にはRAMとの衝突回避のためにひと工夫必要になったのですが、詳細は後程。