あんたCPUなんか創ってどうするのよ?! Vol.1 第4章 第3節

~TD4とかいうCPUがあまりにも残念だったので拡張してみた~

2016/8/14

コミックマーケット C90 3日目 西g16b

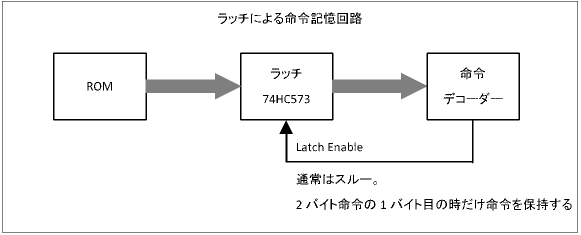

第4章 第3節 命令ラッチの追加

可変長命令を実現する上で厄介なのは、今現在実行している命令をどこかで管理する必要がある点です。なぜなら命令を実行できるのは命令全体を読み込んだ後、つまり2バイト目を読み込んだ時点であり、何もしなければ命令の1バイト目はどこかに忘れ去られてしまうからです。

TD4は全ての命令が1バイトの固定長ため、命令を読み込んだらすぐに実行してしまいます。そのため現在実行中の命令は、プログラムカウンタが指し示している命令だと分かっています。今読みこんだ命令を今実行すればよいので、現在実行中の命令をどこかに覚えさせておく必要はありません。

TD4EX2では命令の1バイト目をラッチ(一時的な記憶回路)に覚えさせます。そうすることで命令の2バイト目を読み込んだ時点でも実行中の命令を忘れないようにします。

ラッチには74HC573というICを使用しました。理由は以下のとおりです。

- 入手が容易

- 非同期動作である

- 8ビットのラッチなので、命令の1バイト目を1個のICで記憶できる

- 出力を停止できる(出力端子をハイインピーダンスにできる)

このうち4番目の出力停止機能はTD4EX2には無関係です。しかし将来必要になりそうな気がするので条件に挙げました。

いっぽう2番目の非同期動作は絶対必要な条件です。これは元々のTD4の動作をできる限り変えずに拡張するためはどうしても必要でした。なぜならこのラッチはROMと命令デコーダーの間に入るため、ここのタイミングが変わると命令デコーダーはもちろんCPU全体のタイミングが変わってしまい、1命令1クロックと言うTD4の元々の設計が変わってしまうからです。

74HC573というICはLE(Latch Enable)という端子によってデータを保存するかどうかを制御しますが、非同期動作であるため、LE端子がイネーブル(H状態)の間は入力端子の状態がそのまま出力端子にスルーされるという特徴があります。このICをROMと命令デコーダーの間に挿入すると、LE端子がイネーブルの間は従来のTD4と全く同じ動作をするようになります。

そしてジャンプ命令や条件ジャンプ命令の場合はLE端子をディセーブル(L状態)にすることで命令を保持させ、命令の実行を完了するまでその状態を続けます。